La integración heterogénea es la clave del futuro de la informática. Aquí, el factor limitante suele ser la densidad de interconexión (pitch), así como el ancho de banda y el consumo de energía. De hecho, a medida que avanzamos hacia plataformas en las que se integran varias matrices, potencialmente de diferentes fundiciones, en el mismo paquete, la cuestión se vuelve extremadamente importante porque la comunicación entre matrices se convierte en el cuello de botella.

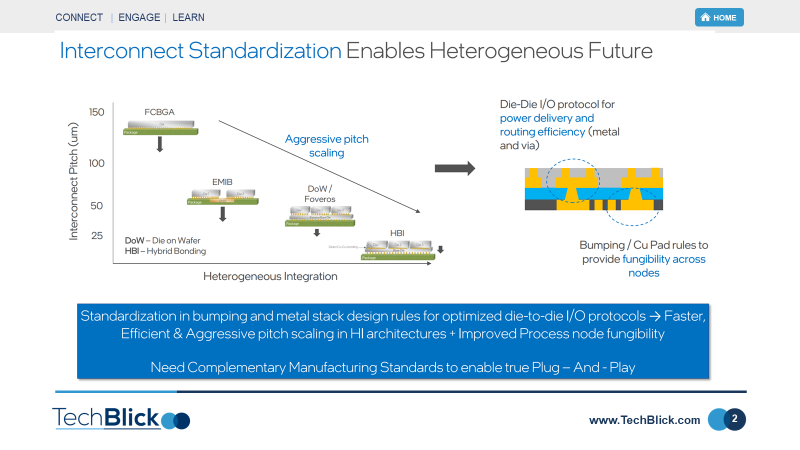

La primera diapositiva de abajo es de Intel, presentada en una conferencia en septiembre de 2021 en línea. Aquí se puede ver la evolución prevista de la tecnología. Primero se lanzó el EMIB. En este caso, un puente de silicio con pasos de <55um sirve como enlace de comunicación pequeño (de 2x2mm a 8x8mm) entre dos troqueles separados en un paquete. Este enfoque es una alternativa a la tecnología estándar de interposición de silicio. A continuación se desarrolló la plataforma Foveros, que permite la integración cara a cara de matrices de diferentes fundiciones en un paquete, todas ellas conectadas a través de una matriz lógica de base de silicio. Como se puede ver, esta tecnología implicará un escalado agresivo y una posible transición a la unión directa de Cu a Cu desde los microbumps.

La segunda diapositiva muestra esta tendencia con más detalle. Muestra la evolución del paso de interconexión a medida que avanza la integración heterogénea. La tecnología común es la de los flip chip BGA (FCBGA). En este caso, el paso está limitado a más de 120um. A continuación, se lanzó el EMIB. Aquí, el paso se redujo a 55um gracias a la tecnología de puente de silicio. Ahora existe Fovereos, que se basa en la tecnología die on wafer. La próxima generación se basará en HBI o unión híbrida

Estas plataformas de integración heterogéneas pueden permitir la integración de matrices de diferentes fundiciones. Sin embargo, el reto es que cada fundición tiene sus propios diseños de E/S, lo que dificulta la compatibilidad. Es conveniente que la industria desarrolle estándares comunes que permitan una solución plug-and-play

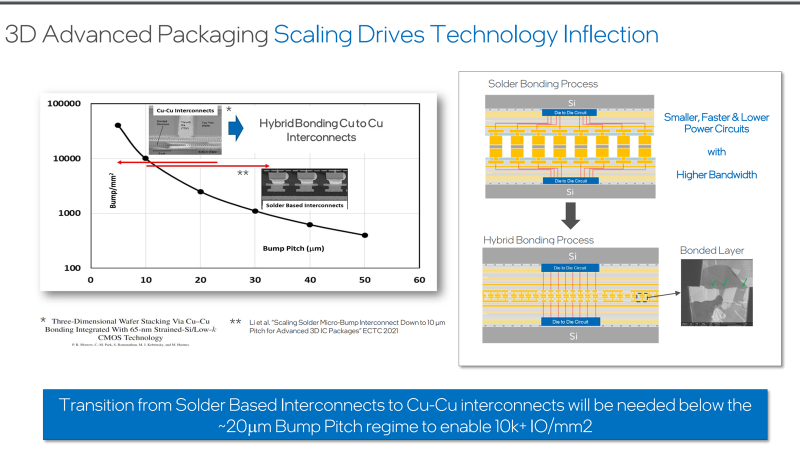

La tercera diapositiva muestra la necesidad de transición hacia la unión Cu-Cu. Como muestra el gráfico de la izquierda, los microbots basados en la soldadura pueden soportar la tecnología hasta alrededor de 15-20um. Más allá de este nivel de paso, se hace necesaria la transición a la unión Cu-Cu. Esta transición ofrece la posibilidad de aumentar la densidad de bump a más de 10000/mm2. Esto es vital para que el tamaño de las E/S y el ancho de banda no limiten el rendimiento global del sistema en los complejos paquetes de varios chips.

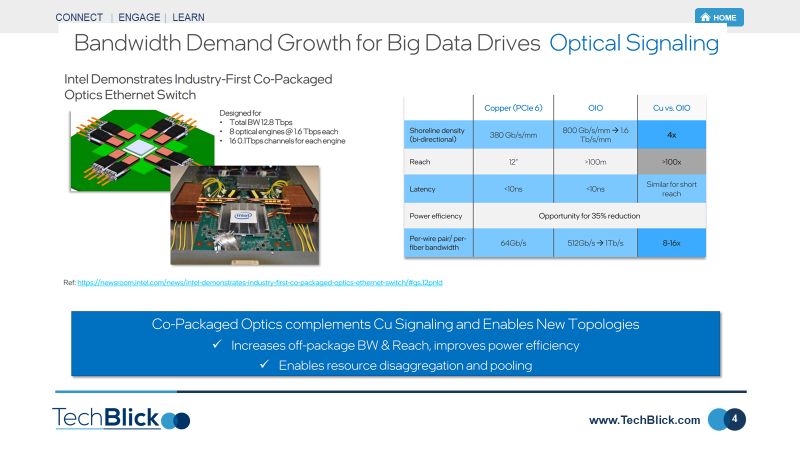

Pero, ¿será todo suficiente? La cuarta diapositiva muestra la necesidad de pasar de la unión de Cu a las tecnologías de E/S ópticas. Como muestra la tabla comparativa, la E/S óptica (OIO) puede multiplicar por 4 la densidad de costa, alcanzando 1,6 Tb/s/mm. También mejorará la eficiencia energética en un 35% aproximadamente.

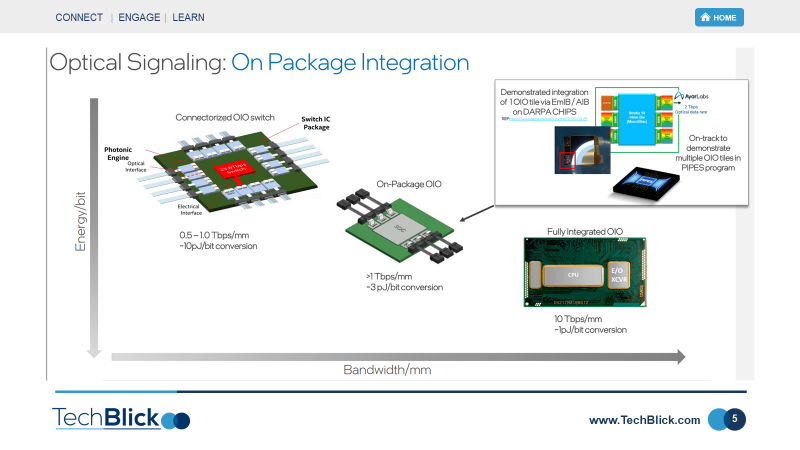

Por último, como se muestra en la quinta y última diapositiva, esta tecnología tendrá que evolucionar. La demostración actual (septiembre de 2021) fue para un OIO en paquete capaz de alcanzar >1Tpbs/mm @ 6 pJ/bit. El objetivo es un OIO totalmente integrado capaz de alcanzar 10 Tbps/mm a sólo 1pJ/bit de conversación.

La integración heterogénea es EL espacio tecnológico a seguir

[This is automatically translated from English]