L'intégration hétérogène est la clé de l'avenir de l'informatique. Ici, le facteur limitant est souvent la densité d'interconnexion (pitch) ainsi que la bande passante et la consommation d'énergie. En effet, à mesure que nous nous dirigeons vers des plates-formes où plusieurs matrices, provenant potentiellement de différents fondeurs, sont toutes intégrées dans le même boîtier, la question devient extrêmement importante car la communication entre matrices devient le goulot d'étranglement.

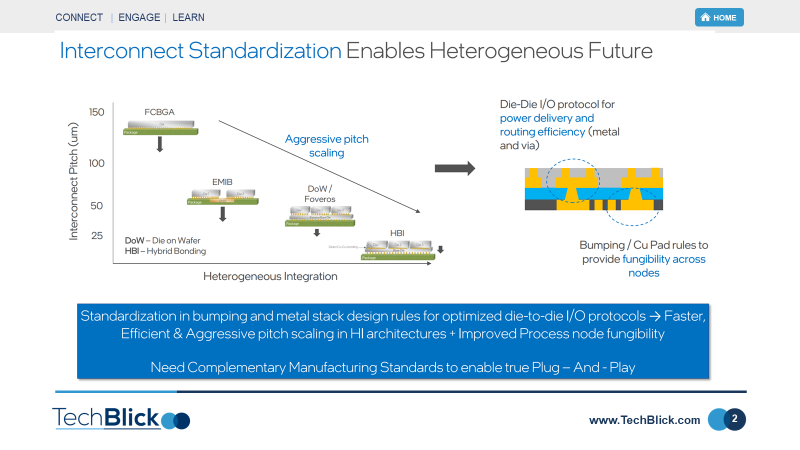

La première diapositive ci-dessous provient d'Intel, présentée lors d'une conférence en ligne en septembre 2021. Vous pouvez y voir l'évolution prévue de la technologie. Tout d'abord, EMIB a été lancé. Ici, un pont en silicium avec des pas de <55um sert de petit (2x2mm à 8x8mm) lien de communication entre deux matrices séparées dans un paquet. Cette approche est une alternative à la technologie standard d'interposition du silicium. Vient ensuite le développement de la plate-forme Foveros, qui permet l'intégration face à face de puces de différentes fonderies dans un boîtier, toutes reliées par une puce logique de base en silicium. Comme vous pouvez le voir, ces technologies impliqueront une mise à l'échelle agressive des pas et une transition potentielle vers un collage direct Cu-Cu à partir de microbilles.

La deuxième diapositive illustre davantage cette tendance. Elle montre l'évolution du pas des interconnexions au fur et à mesure que l'intégration hétérogène progresse. La technologie courante est le flip chip BGA (FCBGA). Le pas est ici limité à environ >120um. Ensuite, l'EMIB a été lancé. Ici, le pitch a été réduit à 55um grâce à la technologie du pont de silicium. Maintenant, il y a Fovereos qui est basé sur la technologie die on wafer. La prochaine génération sera basée sur le HBI ou collage hybride.

Ces plateformes d'intégration hétérogènes peuvent permettre l'intégration de puces provenant de différentes fonderies. Le défi est cependant que chaque fonderie a ses propres conceptions d'E/S, ce qui rend la compatibilité difficile. Il est utile pour l'industrie de développer des normes communes pour permettre une solution plug-and-play.

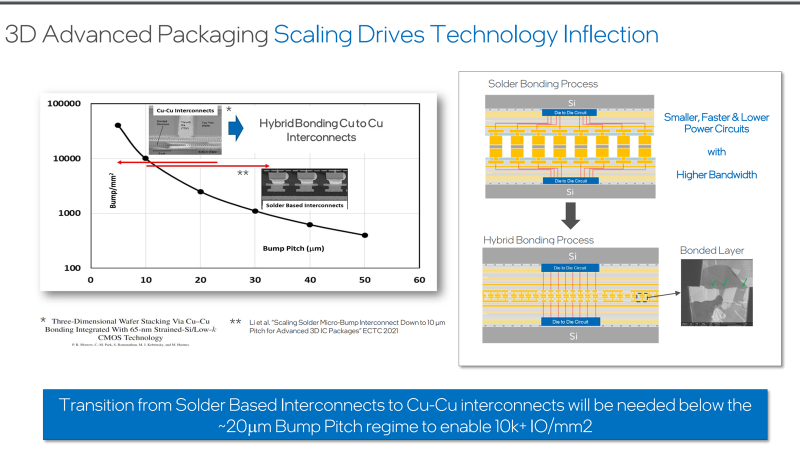

La troisième diapositive montre la nécessité d'une transition vers le collage Cu-Cu. Comme le montre le graphique de gauche, les microbilles à base de soudure peuvent supporter la technologie jusqu'à environ 15-20um. Au-delà de ce niveau de pas, une transition vers le collage Cu-Cu devient nécessaire. Cette transition offre la possibilité d'augmenter la densité de bosse à plus de 10000/mm2. C'est essentiel pour que la taille et la largeur de bande des E/S ne limitent pas les performances globales du système dans les boîtiers complexes à plusieurs puces.

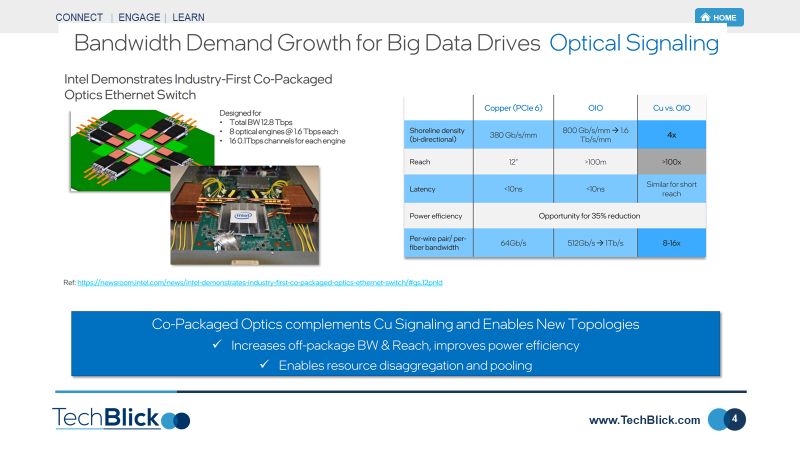

Mais tout cela suffira-t-il ? La quatrième diapositive montre la nécessité de passer de la liaison Cu aux technologies d'E/S optiques. Comme le montre le tableau comparatif, les E/S optiques (OIO) peuvent augmenter la densité de la ligne de rive par un facteur de 4, pour atteindre 1,6 Tb/s/mm. Elle améliorera également l'efficacité énergétique d'environ 35 %.

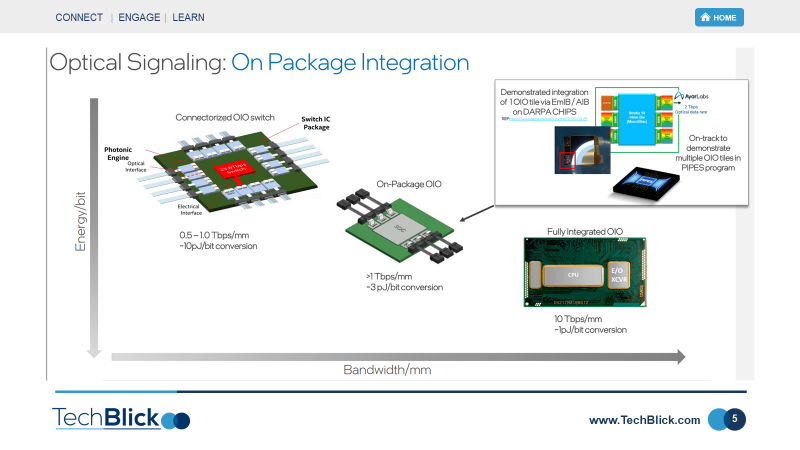

Enfin, comme le montre la cinquième et dernière diapositive, cette technologie devra évoluer. La démonstration actuelle (septembre 2021) portait sur une OIO sur boîtier capable d'atteindre >1Tpbs/mm @ 6 pJ/bit. L'objectif est une OIO entièrement intégrée capable d'atteindre 10 Tbps/mm à seulement 1 pJ/bit de conversation.

L'intégration hétérogène est LE secteur technologique à surveiller [This is automatically translated from English]