In this article series, we will highlight various innovation trends in the diverse area of printed, hybrid, in-mold, and 3D electronics. Our goal is to demonstrate progress and state-of-the-art on various fronts ranging from R2R on-paper printing to thin ICs to conductive inks to stretchable substrates to in-mold electronics and beyond. This article showcases works from S&S, Enjet, CPI, Parsons, ARM, American Semiconductor, Agfa, Nanogate, and CEA-LETI. In the subsequent articles, we will cover developments at Signify, Jabil, Jones Healthcare Packaging, Swarovski, Wuerth, Ntrium, Sunew, XTPL, Identiv, Brilliant Matters, Philips 66, Alpha Assembly, GE Research, ACI, Panasonic, Safi-Tech, DuPont Teijin, VSParticle, Meta, NovaCentrix, Applied Materials, HP, Nano Ops, Brewer Science, e2ip, PolyIC, Kundisch, FIAT, Geely, and many others.

You can learn the details of all these innovations by becoming a TechBlick member. Indeed, by becoming a TechBlick Annual Pass, holder you will benefit from all-year-around learning, training, and networking on emerging technologies. You will have access, for 12 months, to participate in all our LIVE in-person virtual events, catch up with content using our library of on-demand content, and learn from industry experts using our portfolio of masterclasses.

Please take advantage to explore our masterclasses and library of on-demand content.

Upcoming events

13-15 October:

(1) Electronic Textiles & Skin Patches: Hardware & Software

(2) Wearables Sensors & Continuous Vital Signs Monitoring

(3) Printed & Flexible Sensors & Actuators

1 - 2 December

(1) Battery Materials: Next-Gen & Beyond Lithium Ion

(2) Photovoltaics: Perovskite, Organic, Hybrid, & Other Next Generation Technologies

(3) Solid-State Batteries: Innovations, Promising Start-ups, Future Roadmap

Q1 2022:

Frontier Material Innovations: AI in Materials, 3D Printing Materials, and 5G/6G Materials

The agenda for our 13-15 Oct co-located events will be announced next week.

Speakers will include Roche, Medtronics, Ypsomed, Siemens, Microsoft, Jabil, MAS Holding, Williot, Ravensburger, innoME, Trelleborg, Neurosof Bioelectronics, Nutroimcs, Henkel, DuPont, Neteera, Feetme, Binah, Sonde Health, ZSK, Eastprint, VieLight, Atcor, Quad Industries, and many more.

Towards Thin & Flexible Logic

An interesting trend is the development of flexible and ultrathin silicon chips.

One approach is developed by CEA-LETI focusing on thin silicon dies embedded in flex. The process flow is shown below. Here, the silicon wafer is prepared, and a sacrificial layer formed. The flexible layer is coated, the metal lines and bumping pads are prepared, the dies are flip chipped face-down and collectively thinned down. Finally, the top flex layer is added before defining and releasing the thin silicon layer embedded in a flex substrate.

The image below also shows a cross-sectional image, giving a sense of the materials and the dimensions involved. The flexible material is a siloxane material (SINR) enabling photolithography, low-T curing at 80C, and deposition by vacuum lamination.

A key advantage of this process is that potentially any chip, with any number of pins and even with very small pitches, can be supported. This is because the wafer-level-manufactured metallization lines essentially act as a re-distribution layer, fanning out the die pins into large areas accessible to resolutions achieved by printed electronics.

We also highlight some application examples in the image below. Here, one can see an RFID tag with a printed antenna and the RFID chip embedded in flex. This was demonstrated both on a PEN and a polyurethane substrate.

This image panel was constructed from a LIVE talk given at TechBlick (May 2021) by CEA-LETI. Become an Annual Pass holder to watch this content on-demand.

Another interesting approach is taken by American Semiconductor. Here, the CMOS wafer from any IDM or foundry can be thinned and packaged in a PI layer, as shown below. In simplistic terms, the top layer is covered by PI and bump or RDL (re-distribution layer), a temporary carrier is added before the underlying bulk silicon is removed (leaving around 10µm of Si for active circuits), and the backside polymer is added. Finally, the temporary carrier is removed, and the thin SoP silicon chip is mounted on a tape for further processing. The inset shows the thinness of such packaged dies compared even with classic bare dies.

This image panel was constructed from a LIVE talk given at TechBlick (May 2021) by American Semiconductor. Become an Annual Pass holder to watch this content on-demand.

One limitation for this thinned die approach is the resolution incompatibility of silicon chips, i.e., their pad size and pitch, with that of printing techniques. Indeed, using the process above, most CMOS wafers can be processed and packaged, but they could not always be connected to the next level, i.e., the PCB or equivalent. To overcome this challenge, a type of fan-out RDL may be required. An approach is shown below. First, a circuit on a flexible PCB is created using printed conductors and dielectrics. Conductive materials such as ACA or ACF are added and the bumped SoP IC is face-down flip chipped into place. The top cover layer is then laminated or coated. The impact of this approach is also shown below. One starts with a 3.8x3.8 mm SoP Bluetooth IC (AS-NRF51 in this case). Next, the flexible substrate is the created. In this case, it is designed to support 100µm pitch. Finally, the SoP is flip chipped face-down and inserted into the flexible fan-out RDL, creating the final product. This is an elegant approach that enables one to bring the power of silicon ICs into flexible hybrid electronics. However, it is not without its limitations today. In general, the pad pitch in FPCBs, even with expensive Cu on PI, is limited to 25 µm /25µm, whereas many CMOS chips have pad pitches or other space features below this size. As such, there is a limited choice of compatible ICs unless either ultrahigh printing techniques improve the pad pitch resolution and/or the silicon industry offers a wide selection of compatible processes. The latter will progress slowly as this is still a small market.

This image panel was constructed from a LIVE talk given at TechBlick (May 2021) by American Semiconductor. Become an Annual Pass holder to watch this content on-demand.

32-bit Natively Flexible ARM Processor

Back to contents

Finally, on this theme, we would like to cover the latest results reported by Arm and PramatIC in Nature (June 2021) on their natively flexible microprocessors. This is an important progress as it reports a 32-bit ARM microprocess made on the natively flexible IGZO TFTs made on a 0.8µm node. In total, there are 39,157 TFTs and 17,183 resistors in this 59.2mm2 die. This is exciting because, unlike the other approaches reported above, it is a natively flexible IC based on TFT and not silicon wafer technology. It is claimed with good reason that the manufacturing of the IGZO TFTs, based on traditional lithography based TFT production methods, is very cost effectively compared to silicon wafer production, allowing one to bring powerful processing capability to everyday objects on the trillions scale. It is argued that the other approaches cannot have the same cost structure as they are based on standard silicon wafer technology plus additional processing/converting costs.

This image panel was constructed from the Nature paper published on 22 July 2021 by Arm. Note that Arm also presented LIVE at TechBlick (May 2021). Sign up to watch this content on-demand. To learn more join our LIVE(online) event with an Annual Pass.

ElectroHydroDynamic Printing (EHD): Breaking the Limits of Inkjet

Back to contents

EHD is an important development in ultra-precision digital printing of functional material as it can break the resolution limits of conventional inkjet print heads. We will not go into the details of the operational mechanism. Instead, we simply highlight the capabilities as well as the potential applications of this technique.

The image panel below, assembled from an Enjet presentation in May 2021 at TechBlick, demonstrates the range of capabilities. First note how the technique can control the drop size from small to large. Indeed, it can print features from 1 to 100 micron meters. Next, note how it can be used to print various L/S (linewidth/spacing) ratios, covering 2/2, 25/25, and 80/80 µm. Finally, notice how it can print over non-flat and 3D topographies with good step coverage. In short, it can offer digitally controlled deposition of ultrafine features over flat as well as non-flat surfaces.

This image panel was constructed from a LIVE talk given at TechBlick (May 2021) by CEA-LETI. Become an Annual Pass holder to watch this content on-demand.

The next question might be what could be the applications for EHD printing. The image panel below, assembled mainly from the works of Enjet, shows various possibility. In the top right (image a), the TFT repair application is shown. Here a <2µm bridge pattern with good adhesion to TFT surface and low contact resistance can be printed, enabling the repair of defects on TFT panels to boost production yield. This is an excellent technique playing on the strengths of EHD.

Another application could be in micro pad printing for microLEDs (image b). In general, microLEDs will shrink in size as the industry learns to manufacture ever smaller micro-LEDs without scarifying efficiency and as the industry learns to transfer with good yield and economics ever higher numbers of LEDs. In my view, this trend will take time but has an air of inevitability to it. When microLEDs become small, the use of ultraprecise EHD printing for pad deposition over large areas might make sense, especially if one can demonstrate scaled-up and consistent industrial multi-head printing with EHDs. Scrona, from Zurich, is developing such EHD print heads.

Another application could be in QD printing, especially on small-sized micro-LEDs or in high-PPI small-pixel displays. An example is shown below. Here, the pixel size is 20x100µm. Other opportunities include conformal EMI shielding with selective mask-free coverage and creation of precise 3D electrodes wrapping around the edge of the display mother glass.

This image panel was constructed from a LIVE talk given at TechBlick (May 2021) by Enjet. Become an Annual Pass holder to watch this content on-demand.

Silver Nanoparticle Inks: low-T Curing, IME-Compatibility & Transparent Heating Applications

Back to contents

Agfa has been developing a scalable process for mass production of silver nanoparticle inks for some years now. It has a wide portfolio covering screen and inkjet printing inks. Last year it expanded its portfolio by acquiring Clariant’s Ag NP ink technology, allowing it to offer water-based as well as solvent-based inks. Despite being around for a long time, silver nanoparticle inks still continue to show significant improvements. The chart below shows an incremental, but important, evolution. Here, we can see how the resistance of Ag inks have improved for a given curing temperature. The effect is most dramatic for 110C curing but is still substantial for 130C and even 150C. This is good progress as it widens compatibility with low-T substrates and applications. Another interest point in the image below is that Ag nanoparticle inks can also be compatible with in-mold electronics (IME), provided only mild radiuses of curvature are involved. This is interesting as most IME examples utilize screen printed functional sheets. This, however, shows that digital functional printing could also be combined with IME techniques. If there is demand, one can expect that future technical developments will ensure also compatibility with smaller radiuses of curvature too.

This image panel was constructed from a LIVE talk given at TechBlick (May 2021) by Agfa and Nanogate. The right image shows the thermoformed inkjet printed silver nanoparticle inks. Become an Annual Pass holder to watch this content on-demand.

An interesting application is in transparent heating of photochromic motocycle visors. One challenge is that in certain cases the rate of change of colour for the photochromic visor needs to be accelerated by the use of heat. A conventional solution might have been to use CNTs or ITOs as the heating element. In this case, experiments showed that heating was too slow due to high sheet resistance and the heating was non-uniform (see below top right). In these cases, up to 40 seconds might be required to affect the required colour change. However, with inkjet printed Ag NP metal mesh the colour changes was accelerated and uniform under similar conditions (10 seconds was enough). As shown below, the heater consists of a inkjet printed metal mesh with 2mm pitch and 70µm linewidth. This was co-developed with Nanogate. This is an excellent solution and perhaps the only shortcoming is the high reflection of Ag inks which could be dampened with further processing, controlled oxidisation, or other techniques.

This image panel was constructed from a LIVE talk given at TechBlick (May 2021) by Agfa and Nanogate. The top right image shows a sample photochromic motorcycle visor. The top left images show the heating uniformity with IJP Ag NP metal mesh. The bottom right shows the test properties and the characteristics of the IJP Ag NP metal mesh. Finally, the bottom left shows the poor heating uniformity and the slow heating time for the case with other transparent conducting layer solutions. Become an Annual Pass holders to catch up with all on-demand content, participate in masterclasses, and join our in-person virtual events for 12 months. To learn more join our LIVE(online) event with an Annual Pass.

Print-on-Paper: Towards R2R Printing of Multi-Chip Multi-Layer Circuits

Back to contents

The common choice is PI for conventional FPCBs, and it is PET for the emerging flexible hybrid electronics. These choices are however both based on plastics. To eliminate plastic, one can switch to paper. This, however, requires extensive development across the printing technique, material selection, and process know-how. It is not easy.

S&S in Taiwan however has been working on the development of a R2R print-on-paper electronics since 2015, accumulating deep expertise. It has used more than 20 tons of paper from different suppliers and tested more than 100Kg of inks based on different filler materials and for printing techniques. Furthermore, it has also utilized 1M RFID components.

The schematic below shows roughly their configurable set-up (image of pick and place and chip assembling is excluded). S&S uses flexographic and screen printing for higher volumes (e.g., 10M RFID antennas) and inkjet for prototyping and small-scale production (<100k RFID antennas). The curing for mass production is NIR + Photonics, enabling them to achieve some 20 m/min curing speed.

The images above are from a presentation given by S&S at TechBlick in May 2021. Become an Annual Pass holder to watch this content on-demand.

In the simplest case, S&S has begun to R2R manufacture NFC on paper. These NFCs were at least 2x the price of their conventionally manufactured on-plastic counterparts two years ago. Now, S&S indicates, price parity is reached, which can help render more markets accessible.

Importantly, this is also the beginning of the technical development. The NFC antennas have one small chip and a single metallization layer. As shown below, the future will be developing towards more chips, more layers, and more complicated circuit designs. The examples below show the integration of a 2-chip (NFC and LED chips) tag, the development of an 11-component piece (2 active layers and 10 passive components), and the demonstration of a 6-layer tag R2R printed on paper.

This is a very promising trend overall. The manufacturing facility for flexible hybrid electronics (FHE) is still in its relatively early stages of developments but is advancing.

The images above are from a presentation given by S&S at TechBlick in May 2021. Become an Annual Pass holder to watch this content on-demand.

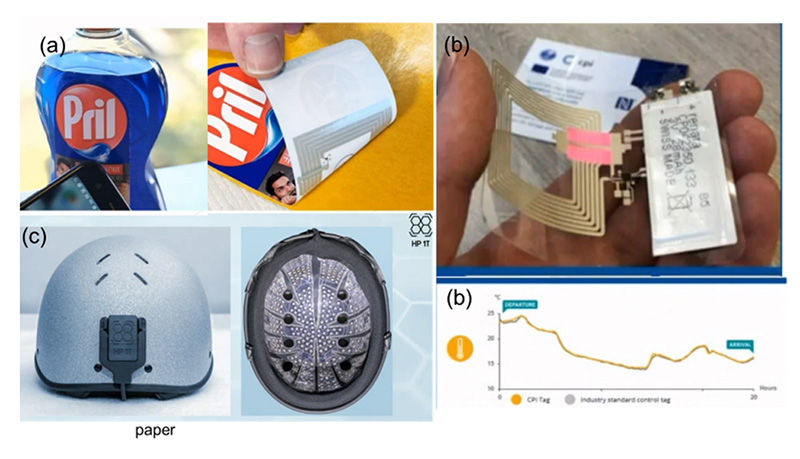

S&S is not alone in developing on-paper electronics. CPI, in the UK, together with various partners, has also demonstrated NFC tags R2R printed on paper. The top right picture below (a) shows an example of a R2R printed paper-based smart label. Here, conductive inks and adhesives were R2R printed using a rotary slot die with optical alignment. The assembly of the electronic chips, the converting, and the testing all took place in a R2R fashion too.

The images above are from a presentation given by CPI at TechBlick in May 2021. This presentation is available on-demand here. The bottom left image (c) is a prototype of a pressure-sensing helmet. Here, an array of printed pressure sensors (probably piezoresistive materials) is conformally attached to the 3D surface of the helmet. The right picture (b) is an example of R2R flexible hybrid electronics show a moisture and temperature monitoring label used in pharma supply chain. CPI manufactured 5000 samples.

Printed Hybrid Arduino-Type Circuits

Back to contents

The image below is an example of a prototype of an Arduino-type circuit which is fully additively manufactured. The work was presented at TechBlick (May 2021) by Parsons. The substrates were made using SLA 3D printing with a Formlabs high-T resin. The active and passive components were then placed into the designated areas and encapsulated using syringe printing. Finally, the silver metallization lines and the dielectric layers were applied on the face-up dies using aerosol jet printing. There is no complex flip chip or RDL layer here as the die-to-board connections are made by conductive lines which bridge the height difference between the die and the board.

Prototype of printed hybrid electronic circuit.

Become an Annual Pass holder to watch this content on-demand.

This seems like a simple prototype, but many technical challenges need to be overcome, especially as the surface is non-flat. In particular, the reliability of the components at interfaces (see below) needs to be tested and guaranteed. A major source of unreliability at these interfaces is the mismatch in the coefficient of thermal expansion of the different materials, which leads to stress build-up during thermal cycling. As shown in the table below, there is a wide range of coefficients involved.

A particular problem area can be the connection to the face-up dies. Here, aerosol deposits dielectric ramps upon which Ag tracks are aerosol printed. The conductive tracks can break, slip off, or disclose. Similarly, conductive tracks across areas filled with adhesives areas can also be a challenge. In this study, Parsons showcased its strategies to carry out reliability tests.

Prototype of printed hybrid electronic circuit.

Become an Annual Pass holder to watch this content on-demand.

Parsons has also worked on printed hybrid electronics to prototype complex re-distribution layers. The aim is to cut down cost and turn-around time of production. One example is shown below (this was not shown at TechBlick). Here, a 5-layer printed RDL is demonstrated. This consists of 11 layers of printed dielectric and conductive layers with 15 separate sintering steps/profiles. The below images also shows the CAD and print patterns in this. When using syringe deposition, a min feature size of 100 µm is the limit. With the uptake of aerosol deposition, this can be reduced to 20 µm. Further techniques such as EHD or microdispensing from XTPL could, in my view, further print down the resolution limit to around 1-5 µm, enabling one to prototype, and perform small production runs of, complex RDL with small feature sizes.

Become a TechBlick Annual Pass holder to benefit from all-year-around learning, training, and networking on emerging technologies. You will have access, for 12 months, to participate in all our LIVE in-person virtual events, catch up with content using our library of on-demand content, and learn from industry experts using our portfolio of masterclasses.

Become an Annual Pass holder to watch this content on-demand.

Visit These Exhibitor Booths During the LIVE Events:

Back to contents

Opmerkingen