Heterogene Integration ist der Schlüssel zur Zukunft der Datenverarbeitung. Der begrenzende Faktor ist hier oft die Verbindungsdichte (Pitch) sowie die Bandbreite und der Energieverbrauch. In dem Maße, in dem wir uns auf Plattformen zubewegen, bei denen mehrere Chips, möglicherweise von verschiedenen Herstellern, in ein und dasselbe Gehäuse integriert werden, wird dieses Thema extrem wichtig, da die Kommunikation von Chip zu Chip zum Engpass wird.

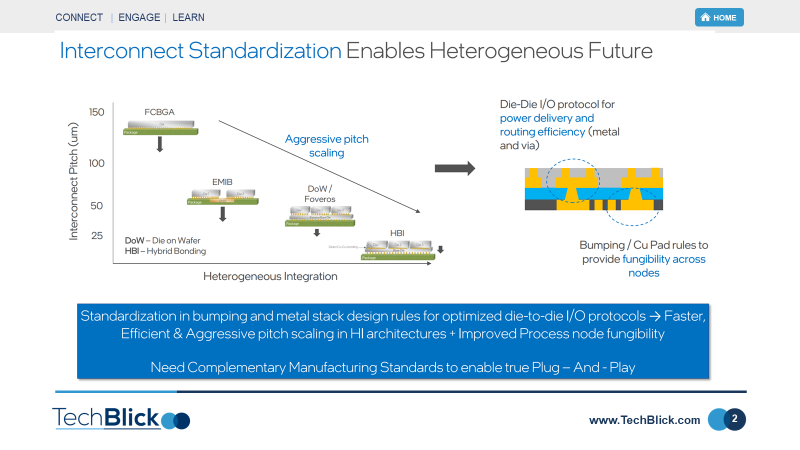

Die erste Folie unten stammt von Intel und wurde auf einer Konferenz im September 2021 online präsentiert. Hier können Sie die geplante Entwicklung der Technologie sehen. Zunächst wurde die EMIB eingeführt. Hier dient eine Siliziumbrücke mit <55um Abstand als kleine (2x2mm bis 8x8mm) Kommunikationsverbindung zwischen zwei separaten Dies in einem Gehäuse. Dieser Ansatz ist eine Alternative zur Standard-Silizium-Interpose-Technologie. Als Nächstes wurde die Foveros-Plattform entwickelt, die eine direkte Integration von Chips verschiedener Hersteller in ein Gehäuse ermöglicht, die alle über einen Silizium-Basislogikchip verbunden sind. Wie Sie sehen können, werden diese Technologien mit einer aggressiven Pitch-Skalierung und einem potenziellen Übergang zum direkten Cu-zu-Cu-Bonden von Microbumps einhergehen.

Die zweite Folie verdeutlicht diesen Trend weiter. Sie zeigt die Entwicklung der Verbindungsabstände im Zuge der fortschreitenden heterogenen Integration. Die gängige Technologie ist Flip-Chip-BGA (FCBGA). Der Pitch ist hier auf etwa >120um begrenzt. Als nächstes wurde das EMIB eingeführt. Hier wurde der Abstand dank der Siliziumbrückentechnologie auf 55 um reduziert. Jetzt gibt es den Fovereos, der auf der Die-on-Wafer-Technologie basiert. Die nächste Generation wird auf HBI oder Hybrid Bonding basieren.

Diese heterogenen Integrationsplattformen können die Integration von Chips aus verschiedenen Foundries ermöglichen. Die Herausforderung besteht jedoch darin, dass jede Foundry ihre eigenen E/A-Designs hat, was die Kompatibilität erschwert. Es ist hilfreich, wenn die Industrie gemeinsame Standards entwickelt, um eine Plug-and-Play-Lösung zu ermöglichen.

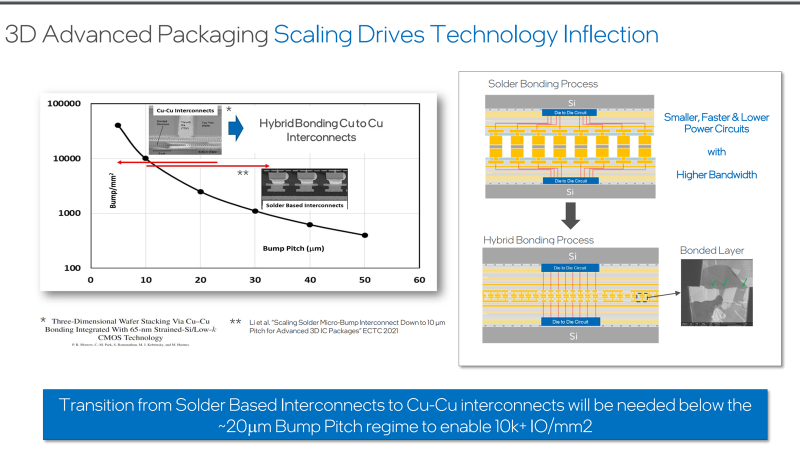

Die dritte Folie zeigt die Notwendigkeit eines Übergangs zur Cu-Cu-Bindung. Wie das linke Diagramm zeigt, können Mikrobumps auf Lötbasis die Technologie bis etwa 15-20 um unterstützen. Jenseits dieses Pitch-Levels wird ein Übergang zum Cu-Cu-Bonden notwendig. Mit diesem Übergang besteht die Möglichkeit, die Bumpdichte auf über 10000/mm2 zu erhöhen. Dies ist von entscheidender Bedeutung, damit die E/A-Größe und -Bandbreite die Gesamtsystemleistung in komplexen Multidie-Gehäusen nicht einschränken.

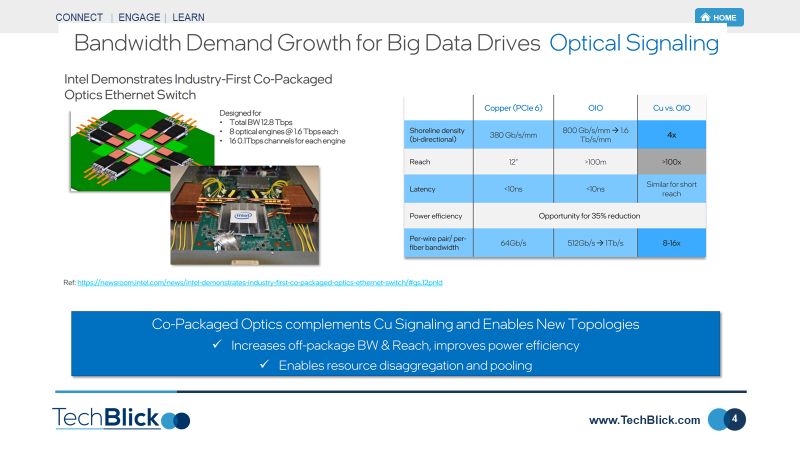

Aber wird das alles ausreichen? Die vierte Folie zeigt, dass ein Übergang vom Cu-Bonding zu optischen E/A-Technologien erforderlich ist. Wie die Vergleichstabelle zeigt, kann die optische E/A (OIO) die Shoreline-Dichte um den Faktor 4 erhöhen und 1,6 Tb/s/mm erreichen. Außerdem wird die Energieeffizienz um etwa 35 % verbessert.

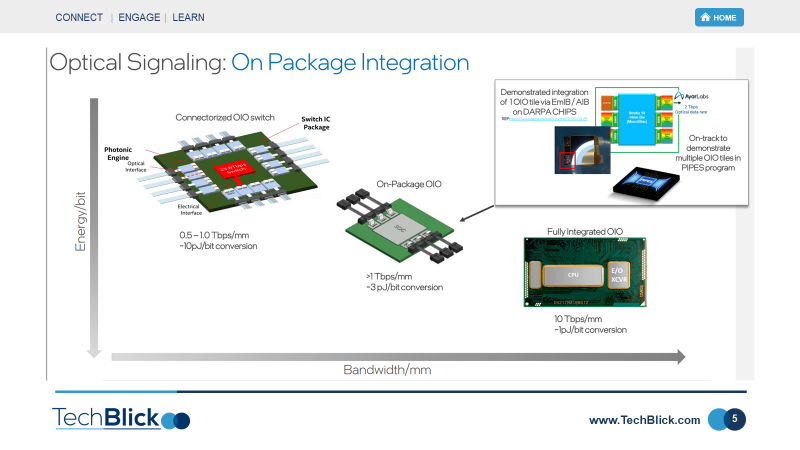

Wie auf der fünften und letzten Folie gezeigt wird, muss diese Technologie weiterentwickelt werden. Die aktuelle (September 2021) Demonstration betraf eine On-Package-OIO, die >1Tpbs/mm bei 6 pJ/Bit erreichen kann. Das Ziel ist eine vollständig integrierte OIO, die 10 Tbps/mm bei nur 1 pJ/Bit erreichen kann.

Heterogene Integration ist DER Technologiebereich, den es zu beobachten gilt [This is automatically translated from English]