ヘテロジニアスインテグレーションは、コンピューティングの未来への鍵である。ここで、制限要因となるのは、インターコネクトの密度(ピッチ)、帯域幅、エネルギー消費量であることが多い。実際、異なるファウンドリの複数のダイをすべて同じパッケージに統合するプラットフォームに移行すると、ダイ間通信がボトルネックになるため、この問題は極めて重要になる。

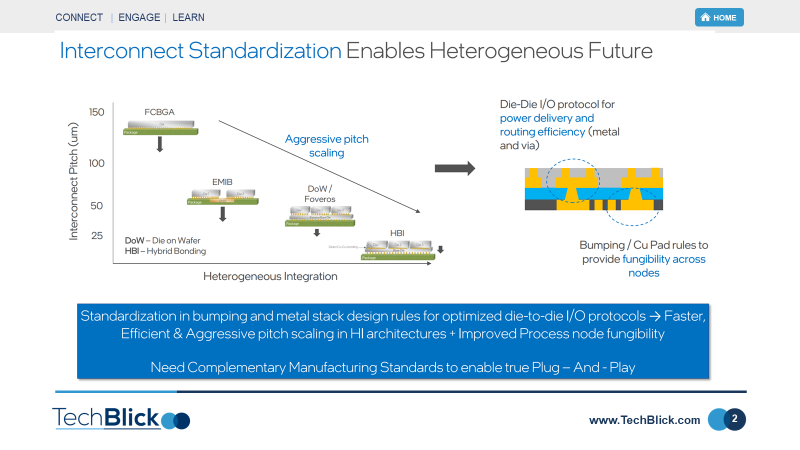

下の最初のスライドは、Intelが2021年9月にオンラインで開催したカンファレンスで発表したものです。ここでは、この技術の意図する進化を見ることができます。まず、EMIBが発売された。ここでは、<55umピッチのシリコンブリッジが、パッケージ内の2つの別々のダイ間の小型(2x2mm~8x8mm)通信リンクとして機能する。これは、標準的なシリコンインターポーズ技術に代わるアプローチである。次に、Foverosプラットフォームが開発され、異なるファウンドリのダイをパッケージ上に対面統合し、シリコンベースのロジックダイで接続することが可能になりました。このように、これらの技術では、積極的なピッチ縮小が行われ、マイクロバンプから Cu-to-Cu 直接接合への移行が予想されます。

2枚目のスライドは、この傾向をさらに詳しく示しています。これは、異種混載の進展に伴うインターコネクトピッチの進化を示したものです。 一般的な技術は、フリップチップBGA(FCBGA)です。ここのピッチは120um超ぐらいが限界です。次に、EMIBが登場した。ここでは、シリコンブリッジ技術により、ピッチは55umに縮小された。現在では、ダイ・オン・ウェハ技術に基づくFovereosがあります。次世代は、HBI(ハイブリッド・ボンディング)がベースとなるでしょう。

これらの異種集積プラットフォームは、異なるファウンドリのダイの集積を可能にします。しかし、ファウンドリごとにI/O設計が異なるため、互換性を確保するのが難しいという課題があります。プラグアンドプレイを可能にする共通規格を開発することは、業界にとって有益なことです。

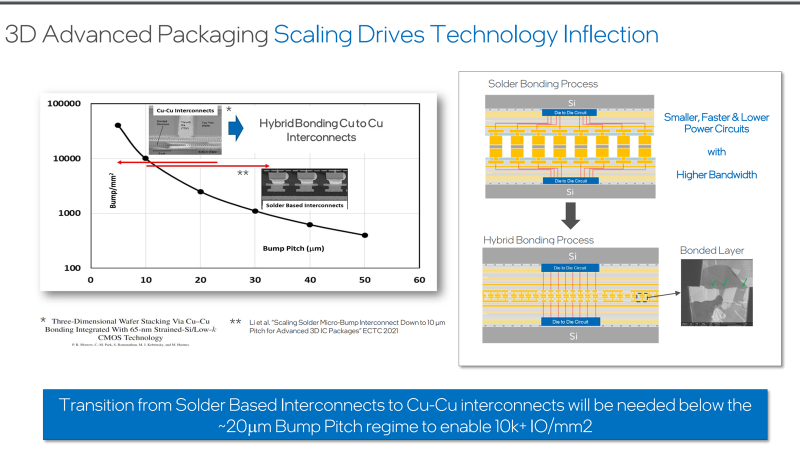

3番目のスライドは、Cu-Cuボンディングへの移行の必要性を示しています。左の図にあるように、15-20um程度までは、はんだベースのマイクロバンプで対応可能です。このピッチを超えると、Cu-Cuボンディングへの移行が必要になってきます。この移行に伴い、バンプ密度を10000/mm2以上まで高めることが可能になります。 これは、複雑なマルチダイパッケージにおいて、I/Oサイズと帯域幅がシステム全体の性能を制限しないようにするために重要なことです。

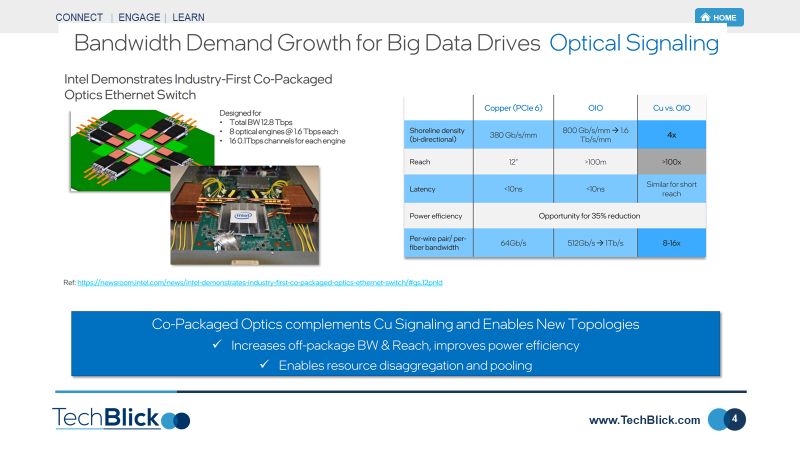

しかし、これでいいのでしょうか?4番目のスライドは、Cuボンディングから光I/O技術への移行の必要性を示している。比較表が示すように、光I/O(Optical I/O)はショアライン密度を4倍に高め、1.6Tb/s/mmに到達することができます。また、電力効率も約35%向上する。

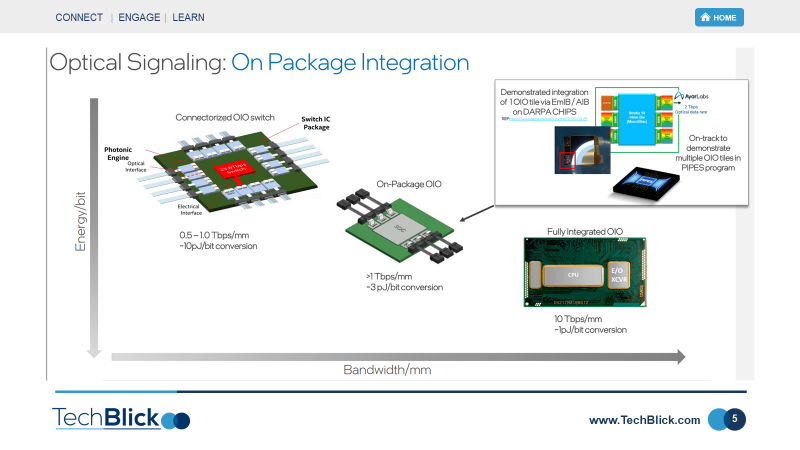

最後に、最後の5枚目のスライドにあるように、この技術は進化していく必要があります。現在(2021 年 9 月)のデモは、1Tpbs/mm 超、6pJ/bit を達成するオンパッケージ型 OIO です。目標は、10Tbps/mm @ 1pJ/bitの会話を実現する完全集積型OIOです。

ヘテロジニアスインテグレーションは注目すべき技術分野です。 [This is automatically translated from English]